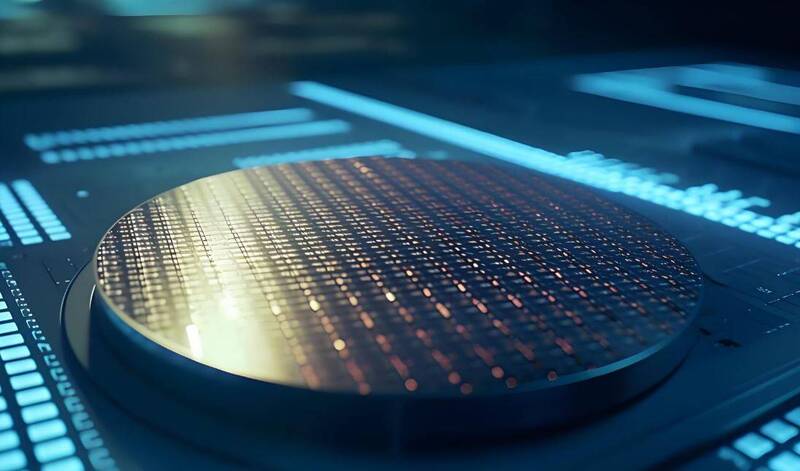

台積電所主導的CoWoS先進封裝技術,已成為美中科技戰的核心之一。(資料照,彭博)

台積電所主導的CoWoS先進封裝技術,已成為美中科技戰的核心之一。(資料照,彭博)

CoWoS適用7奈米以下製程

歐祥義/核稿編輯

〔財經頻道/綜合報導〕近年最熱門的半導體技術,非CoWoS(Chip-on-Wafer-on-Substrate)莫屬。去年台積電業務資深副總經理暨副共同營運長張曉強在台積電新竹場技術論壇中表示,「沒聽過CoWoS,一定是外星人」。張曉強一語道出CoWoS的熱門程度。

摩根士丹利(大摩)最新出具的報告中指出,台積電2026年如何分配CoWoS產能,將是全球AI供應鏈的一個關鍵因素。

市場傳出,為因應CoWoS的訂單供不應求,台積電本計畫考慮赴美、日兩地設立CoWoS廠,以符合當地訂單需求。但現今台積電加速美國布局,除第三期晶圓廠將在6月動土外,下一步將由先進封裝廠接棒,導入CoWoS技術。

分析師指出,台積電(TSMC)在10年前就推出了 CoWoS(Chip-on-Wafer-on-Substrate)技術,在當時是非常冷門的技術,隨著人工智慧(AI)應用快速擴張,晶片製造迎來轉型關鍵期。

據了解,CoWoS是一種先進的半導體封裝技術,主要針對7奈米以下的晶片。CoWoS可進一步拆分為CoW和WoS,CoW就是將晶片堆疊在晶圓上(Chip-on-Wafer),而WoS就是基板上的晶圓(Wafer-on-Substrate)。

CoWoS又分成2.5D與3D版本的封裝技術,其差別在於堆疊的方式不同。2.5D封裝是部分晶片堆疊在基板上,而3D封裝則是全部晶片都堆疊在基板上,其中2.5D封裝是目前主流且可量產的技術。

張曉強表示,CoWoS非常重要,用以整合先進邏輯晶粒和高頻寬記憶體(HBM)。以CoWoS先進封裝技術製作的晶片具有高效能、低功耗的特性,因而成為AI晶片的首選。此外,CoWoS還廣泛應用於高效能運算(HPC)、5G、物聯網和車用電子等領域。

專家直言,先進晶片封裝不只是黏膠,而是精密的跨領域整合。

台積電壟斷高階AI晶片的封裝

數據顯示,全球最高階的CoWoS先進封裝產能,台灣市佔高達9成以上。台積電憑藉其領先業界的CoWoS、InFO、SoIC 等技術平台,幾乎壟斷了高階AI晶片的封裝訂單。但當初台積電研發CoWoS(Chip-on-Wafer-on-Substrate)的初衷,是為了解決高效能晶片在封裝上的「頻寬瓶頸」與「異質整合」問題。

業內人士指出,CoWoS推出迄今,已有3種進化版本, 包括CoWoS-S(Silicon Interposer)到CoWoS-R(Redistribution Layer Based)、CoWoS-L(Large Interposer),CoWoS每一個版本都有它的戰場。

據了解,台積電於2012年正式推出的CoWoS先進封裝技術,主要是針對高頻寬需求,將多顆裸晶(如邏輯+HBM)整合在中介層(interposer)上,當時市場接受度低,主要是因為成本高、製程複雜、良率挑戰大。

以當時的主流晶片仍以SoC單一大晶片為主,並不急需2.5D封裝。因此,應用市場小眾,僅少數高階通訊、網通 ASIC、軍用/科學運算會使用,算是相當冷門的技術。

之後,CoWoS在2017至2020年迎來轉捩點,主要推手是HBM記憶體需求推動。據了解,當時HBM (High Bandwidth Memory) 成為高效能運算 GPU/AI晶片的標配,CoWoS 也成為少數能有效整合邏輯與HBM的封裝方案。當時輝達(NVIDIA)、AMD及Google也導入,這段時期台積電與三星、英特爾在封裝市場競爭開始升溫。

時序進入2023至2025年迄今,隨著AI與HPC需求爆發,CoWoS已經完全主流化。包括輝達H100、H200、B100、GB200都使用CoWoS-L/CoWoS-R封裝。法人指出,GH100到GB200 Interposer(中介層)從原先可切28至29顆降至16顆,未來GR系列只能切割到8顆,為產能緊缺因素之一。

在輝達(NVIDIA)、博通(Broadcom) 和超微等AI 科技巨頭的強勁需求,使得台積電的CoWoS產能供不應求,成為AI加速器晶片放量的一個關鍵因素。

台積電CoWoS產能不能滿足客戶訂單,只能將部分產能外包合作的封裝廠。(彭博)

台積電CoWoS產能不能滿足客戶訂單,只能將部分產能外包合作的封裝廠。(彭博)

台積電CoWoS產能不夠用 外包廠「全面開工」

人工智慧AI應用加速AI晶片和CoWoS先進封裝需求。儘管台積電擴大了CoWoS產能,但CoWoS的需求量太大,因此仍必須將部分產能外包給合作的封裝廠,包括矽品和日月光,這也促使了半導體設備外商在台灣擴大投資,發展先進封裝廊道。

分析師指出,台積電外包CoWoS,主要有3個考量,包括客戶們對高頻寬封裝需求暴增、但自家產能不敷使用,以及為了縮短交期、滿則客戶時程,以及為符合美國、日本本地化封裝政策。

舉例來說,台積電與與Amkor在美國亞利桑那州進行策略性合作,但該廠是由Amkor砸628億元所建,但封裝的是台積電製程晶圓,屬「CoWoS 外包封裝」。另一例子是輝達 H100/H200的某些封裝步驟由日月光處理,但封裝設計與核心堆疊還是由台積電主導。

至於南韓的三星(Samsung)以及專業封測代工(OSAT)龍頭日月光(ASE)及其子公司矽品(SPIL)、美國的艾克爾(Amkor)也積極布局先進封裝,主要產能大多位於亞洲地區。

半導體供應鏈透露,儘管外包OSAT(專業封測代工)廠對於CoWoS都有對應技術,但以輝達採用的CoWoS-L而言,僅有台積電具備相關Know-how。

專家直言,亞洲(尤其台灣)在全球先進封裝市場的絕對主導地位。

台灣具3大先進封裝優勢,在其產業中最具競爭力。(擷取自中國社交平台)

台灣具3大先進封裝優勢,在其產業中最具競爭力。(擷取自中國社交平台)

CoWoS產能吃緊 台積電今年恐漲價

由於CoWoS封裝產能緊俏,摩根士丹利(Morgan Stanley)曾在2024年底預估,台積電將在今年調漲先進封裝報價,有望漲價10-20%,以維持供應穩定。大摩估算,台灣CoWoS平均單位封裝成本,比美國本土便宜約25–35%,即使在封裝價格上調後,依然具吸引力。

根據半導體專業人士的開放論壇《semiwiki》在2024年底的一篇文章指出,輝達引領2025年全球CoWoS市場需求,其63%的總容量將佔據主導地位;緊隨其後的是博通、佔13%,是CoWoS需求的第二大貢獻者。至於AMD和Marvell各佔8%、並列第三,顯示兩家公司對這項技術的興趣相當。

其他貢獻者包括AWS + Alchip(3%)、英特爾(2%)、Xilinx(1%)和其他(3%),其市佔率要小得多,這表明對CoWoS容量的依賴相對有限。

分析師指出,台灣具3大先進封裝優勢,不論是技術成熟度領先全球,在成本也具競爭力,整合度上更是一條龍,是全球先進封裝產業中最具競爭力。至於美國技術仍在起步中,成本也是高昂,整合度上堪稱中等,得與台積電協作,其競爭以政策驅動為主。

日本的先進封裝尚未量產,正在規劃中。分析師預估,其成本效應應該介於中間,但因尚未進行產業整合,未來需觀察JASM封裝廠建設。而南韓三星,其技術成熟,與台積電技術互有高下,但先向自用為主,成本效應介於中間水準,其封裝不外接。

專家直言,儘管台灣在先進封裝上享有技術和成本優勢,但台灣廠商未來恐面臨3大壓力,包括在地緣政治風險下,國際客戶要求分散產能,美國、日本要求在地封裝,恐分流部分台灣訂單。以及台灣電價若進一步上升,恐削弱台灣在先進封裝生產的成本優勢,以及三星與英特爾力拼封裝技術整合,有可能以低價搶市。

一手掌握經濟脈動 點我訂閱自由財經Youtube頻道

免費訂閱《自由體育》電子報熱門賽事、球星動態不漏接

不用抽 不用搶 現在用APP看新聞 保證天天中獎 點我下載APP 按我看活動辦法